Articolo

Porte Logiche senza Porte

Mi rendo conto che potrebbe sembrare lo sproloquio di un alcolista neanche tanto anonimo, ma non è così.

Oggi, ravanando tra tutte le carte conservate alla ricerca di quelle da buttare, ho trovato una stampa di più di un decennio fa con gli schemi delle primissime porte logiche in tecnologia RTL (Resistor Transistor Logic) e le successive DTL (Diode Transistor Logic). Quelle prima delle TTL (Transistor Transistor Logic) tanto per intenderci.

Il bello è che gli ultimi disegni mi sembravano un errore, ma ragionandoci sopra ho scoperto che non era così. Con una sola resistenza e un solo diodo è possibile creare una porta OR e una porta AND a due ingressi che io chiamerei scherzosamente in tecnologia RDL (Resistor Diode Logic). Chissà se esistevano?

A che servono? Semplice, se ci serve una sola porta AND o una sola porta OR, non dobbiamo sprecare un integrato quadruplo TTL ma solo un diodo e una resistenza. Una bella economia non vi pare?

Ve le illustro qui di seguito:

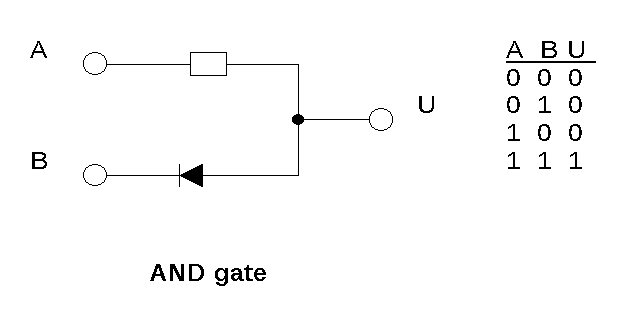

AND gate

In una porta AND a due ingressi A e B, l'uscita A*B andrà a livello alto quando entrambi gli ingressi sono a livello alto.

Vediamo come:

Abbiamo due ingressi, A e B e una uscita U. Usiamo i livelli logici L=0 e H=1.

Se mettiamo a L gli ingressi A e B, ovviamente l'uscita sarà a L non essendoci tensione.

Se mettiamo a L l'ingresso A e a H l'ingresso B, il diodo contropolarizzato non condurrà mentre la resistenza terrà a L l'uscita U.

Se invertiamo i livelli, l'uscita U tenderebbe ad avere il valore H dell'ingresso A ma non potrà perché il diodo polarizzato direttamente sull'ingresso B forzerà a L l'uscita U. O meglio, lo terrà ad una tensione pari alla Vf dello stesso. La Vf deve essere al di sotto di 0,8V che è il massimo valore consentito dai TTL. Un diodo possibile può essere il 1N4150.

Con gli ingressi entrambi a H, l'uscita U sarà ovviamente a H perché il diodo è contropolarizzato e lascerà comandare la resistenza.

OR gate

In una porta OR a due ingressi A e B, l'uscita A+B andrà a livello alto quando almeno un ingresso è a livello alto.

Vediamo come:

Anche in questo caso abbiamo due ingressi, A e B e una uscita U. Usiamo i livelli logici L=0 e H=1.

Se mettiamo a L gli ingressi A e B, ovviamente l'uscita sarà a L non essendoci tensione.

Se mettiamo a L l'ingresso A e a H l'ingresso B, il diodo condurrà e in uscita avremo il livello H.

Se invertiamo i livelli, l'uscita U assumerà il valore H dell'ingresso A ma non potrà essere forzata a zero dall'ingresso B perché il diodo non conduce essendo contropolarizzato.

Con gli ingressi entrambi a H, l'uscita U sarà ovviamente a H.

All news